在数字集成电路设计中,抖动(Jitter)是一个至关重要且普遍存在的现象。它本质上是数字信号边沿相对于理想时序位置的微小、快速、非确定性偏移。这种看似微小的时序偏差,在高速、高精度集成电路中却可能引发灾难性的后果,深刻影响系统的性能、可靠性与稳定性。

抖动的核心成因

抖动的产生源于多种因素的综合作用,主要可归纳为以下几类:

- 内部噪声:这是抖动最根本的来源之一。电路中晶体管的热噪声(约翰逊-奈奎斯特噪声)、闪烁噪声(1/f噪声)以及电源/衬底噪声等,都会直接调制信号的渡越时间,导致边沿到达时刻的随机波动。

- 电源完整性与信号完整性(PI/SI)问题:电源网络的波动(如地弹、电源噪声)会通过器件阈值电压等参数影响开关速度。传输线上的反射、串扰等信号完整性问题会扭曲信号波形,改变其过零点,从而引入确定性抖动。

- 时钟分配网络的不完美:时钟路径上的缓冲器延时偏差、互连线延时差异以及时钟树上的噪声注入,都会导致时钟边沿到达各触发器的时间不一致,即时钟抖动。这是系统级时序违例的主要诱因之一。

- 工艺、电压、温度(PVT)变化:制造工艺的微观差异、工作电压的波动以及环境温度的变化,会导致器件参数(如迁移率、阈值电压)漂移,从而引起信号传播延时的系统性或随机性变化。

抖动对数字电路的影响

抖动的影响是全方位的,其严重性随电路速度的提升而指数级增加:

- 时序违例与功能错误:过大的抖动会侵蚀系统的时序裕量。对于建立时间/保持时间检查,时钟或数据的抖动可能直接导致触发器采样错误,引发功能故障。在高速串行接口(如SerDes)中,抖动会直接缩小数据有效采样窗口,增加误码率。

- 性能降级:为了容忍一定程度的抖动,设计者往往被迫降低系统最高工作频率或增加时钟周期,从而牺牲了性能。

- 功耗增加:在时钟路径中,为了抑制抖动(如使用锁相环PLL进行滤波和抖动衰减),需要增加电路复杂度,这会带来额外的功耗开销。

- 测试与验证挑战:抖动具有随机性和统计特性,使得电路在最坏情况下的时序分析变得异常复杂,增加了设计验证和测试的成本与难度。

集成电路设计中的抖动应对策略

应对抖动是一个贯穿设计始终的系统性工程:

- 设计阶段的建模与预算:在架构和电路设计初期,就需要对整系统的抖动进行建模和预算分配。为时钟发生器、时钟分配网络、数据路径等不同模块设定严格的抖动指标(如周期抖动、周期周期抖动、时间间隔误差)。

- 电路级抑制技术:

- 采用低噪声的电源调节器(如LDO)和精心设计的电源分配网络(PDN),使用大量的去耦电容来滤除高频电源噪声。

- 设计对电源噪声不敏感的电路结构,如差分逻辑、电流模逻辑(CML)或在关键路径上使用高电源抑制比(PSRR)的缓冲器。

- 使用高性能的时钟生成与调理电路,如带抖动衰减功能的低噪声PLL、延迟锁相环(DLL)。

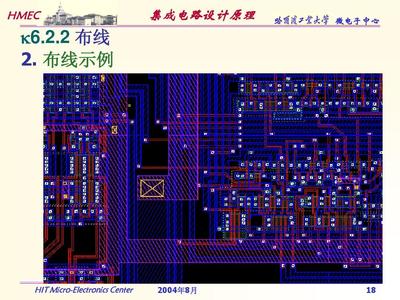

- 布局布线(物理实现)优化:

- 对时钟网络进行对称化、屏蔽和精心的树形结构设计,以最小化偏斜和噪声耦合。

- 确保电源和地网络的低阻抗特性,将敏感模拟/时钟模块与数字开关噪声源进行物理隔离。

- 控制关键信号线的长度、阻抗匹配,减少反射和串扰。

- 系统级与架构级技术:

- 采用弹性电路或容错时序设计,如使用可调延时线、时间借位技术或异步电路设计范式,来吸收或容忍一定范围内的抖动。

- 在高速串行链路中,使用均衡、时钟数据恢复(CDR)电路和先进的编码方案来对抗抖动带来的影响。

抖动是现代数字集成电路设计中一个无法回避的核心挑战。深入理解其物理根源,在设计全流程中对其进行精准的建模、严格的控制与有效的管理,是确保芯片在高速运行下依然稳定可靠的关键所在。随着工艺节点不断演进和系统频率持续攀升,对抖动的分析与控制必将变得更加精细和重要。